На ежегодном симпозиуме СБИС, который состоится на следующей неделе, корпорация Intel представит пару долгожданных докладов о своем прогрессе в разработке новой технологии изготовления микросхем PowerVia — находящейся в разработке компании для реализации тыловых сетей подачи питания. Наряду с технологией Intel RibbonFET для транзисторов с универсальным затвором, PowerVia и RibbonFET призваны стать большим ударом Intel для остальной отрасли кремниевой литографии, представляя вместе две основные чиповые технологии, которые, по мнению Intel, вернут их обратно в прежнее положение. потрясающая руководящая должность. В совокупности эти две технологии станут основой производственных узлов Intel эпохи «ангстремов», которые в следующем году будут запущены в крупносерийное производство, что делает прогресс Intel в новых технологиях очень важным как внутри компании, так и за ее пределами. и тот, который Intel хочет решить.

Когда дело доходит до технологии производства чипов Intel, ставки для научно-исследовательских групп Intel не могут быть выше, чем сейчас. Давний лидер фабрики ошибался бы – неоднократно – и сейчас находится в середине многолетних усилий по корректировке курса, не только для того, чтобы вернуть то лидерское положение, которое они потеряли, но и для того, чтобы ворваться в бизнес по производству микросхем по контракту набирает обороты.

В результате, хотя исследовательские работы СБИС обычно не привлекают большого внимания со стороны, этот год, в частности, является большим исключением. Поскольку RibbonFET и PowerVia должны быть запущены в производство в следующем году, Intel приближается к завершению научно-исследовательских работ по первому поколению этих технологий. В настоящее время Intel находится на том этапе, когда они могут представить своим коллегам в отрасли СБИС свои первые результаты, связанные с созданием сложной логической микросхемы для тестирования. А инвесторам Intel и другим аутсайдерам Intel может показать первое реальное доказательство того, что их усилия по возвращению на правильный путь вполне могут увенчаться успехом, что даст Intel возможность опередить конкурентов, в которых так нуждается компания.

В связи с этим на симпозиуме, который состоится на следующей неделе, Intel собирается раскрыть большой объем информации о своей реализации сетевой технологии тыловой подачи питания, которую они называют PowerVia. Центральное место в этих документах занимает Blue Sky Creek, микросхема логического тестирования, похожая на продукт Intel, которая реализует подачу питания на задней стороне на технологическом процессе Intel 4 с поддержкой EUV. С помощью Blue Sky Creek Intel намерена продемонстрировать не только то, что PowerVia своевременно работает с ЦП для крупносерийного производства в следующем году, но и то, что производительность и производственные преимущества обратной подачи питания — это все, что Intel обещала. Достаточно сказать, что Intel готовится к конференции VLSI в этом году, которая станет очень важным событием для компании.

Предыстория: обратная подача энергии

Задние сети подачи питания (BSP/BS-PDN) — это технологическая концепция, которая в течение последних нескольких лет тихо разрабатывалась во всей отрасли производства микросхем. Подобно EUV в недавних производственных узлах, BS-PDN рассматривается как необходимая технология для продолжения разработки все более совершенных технологий технологических узлов, и в результате ожидается, что все передовые фабрики микросхем перейдут на эту технологию в будущем.

С учетом сказанного, они не все перемещаются туда одновременно. Intel рассчитывает стать первым из трех крупнейших производителей чипов, который внедрит эту технологию в производство, по крайней мере, на два года раньше, чем ее конкуренты. В результате Intel во многом является первооткрывателем технологии, которая не лишена рисков, но также приносит значительные выгоды за правильное использование технологии (и их своевременности). Для Intel компания считает, что это будет их новый момент FinFET — отсылка к представлению Intel FinFET на 22 нм в 2012 году, что закрепило лидерство Intel на рынке на несколько лет. Это особенно важно, поскольку Intel не будет иметь преимущества перед своими конкурентами, когда дело доходит до синхронизации полевых транзисторов (GAAFET), поэтому BS-PDN/PowerVia станет козырной картой Intel в фантастическом пространстве для следующего несколько лет.

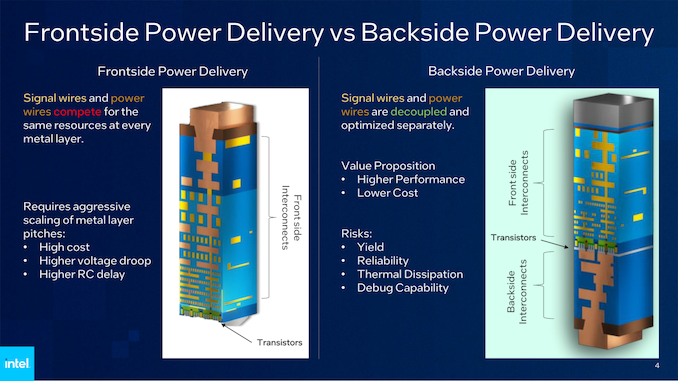

Между тем, чтобы полностью понять, как работает BS-PDN, лучше всего начать с того, чтобы вспомнить, как работает традиционная (внешняя) подача питания, чтобы мы могли сравнить это со многими изменениями, которые происходят при создании пластины BS-PDN.

Процесс производства современной микросхемы подачи питания на лицевой стороне начинается с травления транзисторного слоя M0. Это самый маленький и самый сложный слой на кристалле, и именно здесь больше всего нужны высокоточные инструменты, такие как EUV и мульти-шаблон. Короче говоря, это самый дорогой и сложный слой чипа, который имеет значительные последствия как для конструкции чипов, так и для их тестирования.

Кроме того, добавляются дополнительные металлические слои увеличивающихся размеров, чтобы учесть всю проводку, необходимую между транзисторами и различными частями процессора (кэш, буферы, ускорители), а также обеспечить маршрутизацию для питания, поступающего еще дальше. куча. Intel сравнивает это с приготовлением пиццы, что является грубой аналогией, но эффективной.

Современный высокопроизводительный процессор обычно имеет в своей конструкции от 10 до 20 металлических слоев. В частности, в процессе Intel 4 имеется 16 слоев логики с шагом от 30 до 280 нм. И еще два «гигантских металлических» слоя поверх этого только для разводки питания и размещения внешних разъемов.

После того, как кристалл полностью изготовлен и отполирован, его переворачивают (что делает его перевернутым чипом), чтобы чип мог общаться с внешним миром. Этот переворот помещает все разъемы (питание и данные) в нижнюю часть чипа, а транзисторы — в верхнюю часть чипа. После того, как было освоено производство флип-чипов, отладка и охлаждение чипов стали особенно удобными, поскольку это позволило инструментам отладки легко получить доступ к важнейшему транзисторному слою. Между тем, эти маленькие горячие ворота также стали особенно близко к кулеру чипа, что позволило относительно легко отводить тепло от чипа.

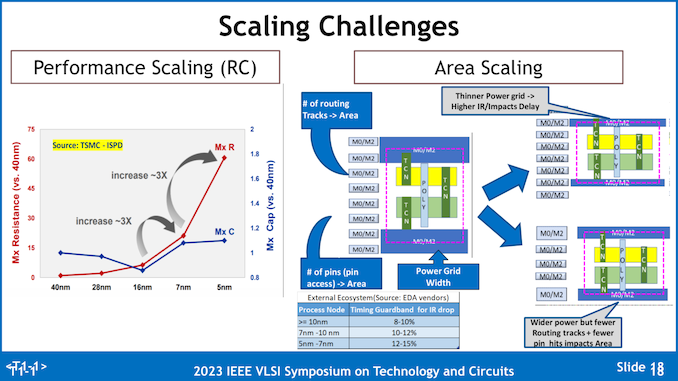

Однако недостатком фронтальной подачи питания является то, что это означает, что и питание, и сигнальные провода находятся на одной стороне чипа. Оба провода должны пройти через более 15 слоев, чтобы добраться до транзисторов, все время конкурируя за ценное пространство и создавая помехи друг другу. В частности, для силовых проводов это особенно неприятно, так как сопротивление вдоль этих проводов вызывает падение напряжения входящей мощности, что известно как эффект IR Drop/Droop.

На протяжении большей части истории изготовления чипов это не было серьезной проблемой. Но, как и многие другие аспекты создания микросхем, проблема становилась все более и более очевидной по мере того, как уменьшались размеры элементов микросхемы. Здесь нет очевидного жесткого ограничения на подачу питания на переднюю сторону, но, учитывая, насколько сложнее сжимать чипы с каждым последующим поколением, проблема стала слишком большой (или, скорее, слишком дорогой), чтобы ее можно было обойти.

И это подводит нас к обратной подаче энергии. Если наличие сигналов и питания на одной стороне чипа вызывает проблемы, почему бы не разделить их? В двух словах, это именно то, что пытается решить подача питания на задней стороне, перемещая все соединения питания на другую сторону пластины.

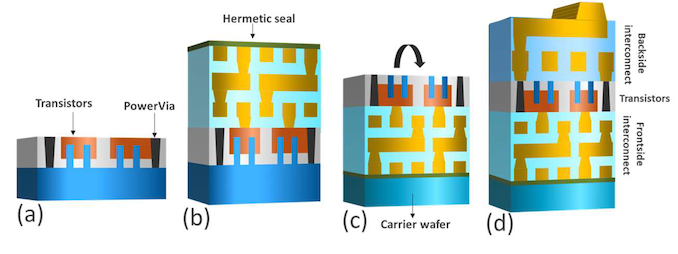

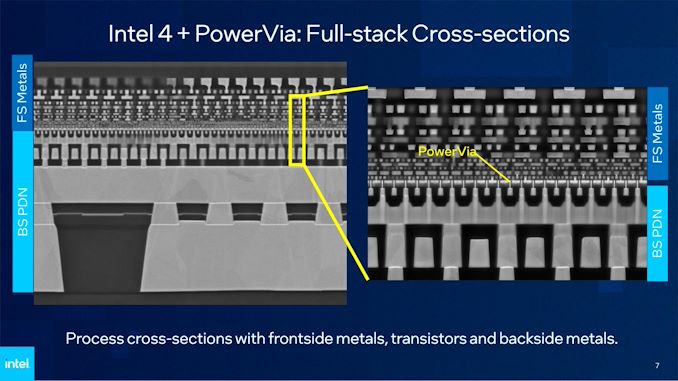

Для реализации этой концепции в Intel PowerVia Intel буквально переворачивает пластину вверх дном и полирует почти весь оставшийся кремний, пока он не достигнет нижней части транзисторного слоя. В этот момент Intel создает металлические слои для подачи питания на противоположной стороне чипа, подобно тому, как раньше они строили их на передней стороне чипа. Конечным результатом является то, что Intel получает по существу двухсторонний чип, с подачей питания на одной стороне и передачей сигналов на другой.

На бумаге (и в документе Intel) переход на BS-PDN дает несколько преимуществ. В первую очередь это существенно влияет на упрощение конструкции микросхемы. Мы немного вернемся к конкретным заявлениям и выводам Intel, но здесь следует особо отметить, что это позволило Intel уменьшить плотность их металлического слоя M0. Вместо того, чтобы требовать шаг 30 нм для Intel 4, тестовый узел Intel для Intel 4 + PowerVia допускал шаг 36 нм. Это напрямую упрощает самый сложный и дорогой этап обработки всего чипа, откатывая его к чему-то более близкому по размеру к процессу Intel 7.

BS-PDN также может обеспечить некоторые скромные улучшения производительности чипов. Сокращение пути подачи питания к транзисторам с помощью чего-то более прямого помогает противодействовать эффекту IR Droop, что приводит к лучшей подаче питания на транзисторный слой. И вывод всех этих проводов подачи питания из сигнальных слоев также улучшает их характеристики, устраняя помехи питания и предоставляя разработчикам микросхем больше возможностей для оптимизации своих конструкций.

В противном случае расплатой за все это является, прежде всего, потеря ранее упомянутых преимуществ создания внешнего чипа. Слой транзистора теперь находится примерно посередине чипа, а не на его конце. Это означает, что традиционные инструменты отладки не могут напрямую проверить транзисторный слой готового чипа, и теперь между транзисторным слоем и системой охлаждения имеется около 15 слоев сигнальных проводов. Это не непреодолимые проблемы, как тщательно изложено в документе Intel, но это были проблемы, которые Intel пришлось обойти при разработке.

Технологичность — это еще один набор компромиссов, связанных с переходом на BS-PDN. Создание силовых слоев на обратной стороне кубика — это то, чего раньше никогда не делали, что увеличивает вероятность того, что что-то пойдет не так. Таким образом, не только подача энергии должна работать, но она должна работать без значительного снижения производительности чипов или иного снижения надежности чипов. Но если все это сработает, то дополнительные усилия по созданию силовых слоев на обратной стороне пластины с лихвой компенсируются экономией времени и средств за счет отсутствия необходимости направлять питание через переднюю сторону.

Дополнительные недостатки Intel: несущие пластины и нано-TSV

Поскольку в свое время внутренние сети доставки электроэнергии станут отраслевым стандартом, мы старались не слишком сосредотачиваться на конкретной реализации Intel BS-PDN/PowerVia. Но теперь, когда мы коснулись основ BS-PDN, стоит отметить пару специфичных для Intel деталей реализации.

Прежде всего, Intel использует несущую пластину как часть процесса создания, чтобы обеспечить жесткость чипа. Приклеенная к лицевой стороне пластины PowerVia после того, как изготовление этой стороны завершено, несущая пластина представляет собой фиктивную пластину, помогающую поддерживать чип, пока Intel работает с другой стороны. Поскольку двусторонний процесс изготовления чипов стирает большую часть оставшейся кремниевой пластины, не так много структурного кремния, чтобы скрепить все это вместе. Как слегка шутит Intel, несмотря на то, что это кремниевая литография, к концу на пластине остается лишь небольшое количество кремния.

Эта несущая пластина, в свою очередь, остается частью чипа до конца его жизни. После завершения изготовления чипа Intel может отполировать связанную несущую пластину до необходимой толщины. Следует отметить, что поскольку несущая пластина находится на сигнальной стороне чипа, это означает, что она представляет собой еще один слой материала между транзисторами и кулером. Методы Intel по улучшению теплопередачи учитывают это, но для энтузиастов ПК, привыкших к транзисторам в верхней части своего чипа, это будет значительным изменением.

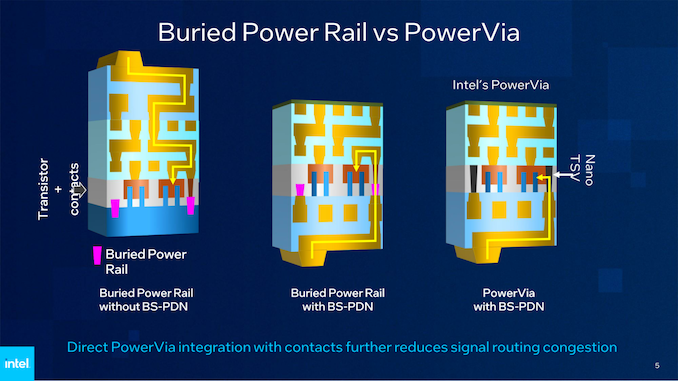

Другой примечательной деталью Intel в реализации BS-PDN является использование TSV для маршрутизации питания. В PowerVia есть наноразмерные TSV (метко названные Nano TSV) в транзисторном слое чипа. Это отличается от скрытых шин питания, которые пионер отрасли IMEC изучает со своими BS-PDN.

Суть в том, что, хотя шины питания по-прежнему должны проходить вверх и вниз по транзисторному слою для подачи питания, использование TSV позволяет доставлять питание более непосредственно на транзисторный уровень. Для Intel это технологическое преимущество, которое они стремятся использовать, поскольку оно избавляет от необходимости разрабатывать и встраивать маршрутизацию, необходимую для скрытых шин питания.

www.anandtech.com