Во вторник JEDEC опубликовал официальные спецификации GDDR7 DRAM, последней версии давнего стандарта памяти для видеокарт и других устройств с графическим процессором. Новейшее поколение GDDR обеспечивает сочетание увеличения объема памяти и пропускной способности памяти, при этом последнее обусловлено в первую очередь переключением на сигнализацию PAM3 на шине памяти. Новейший стандарт графической памяти также увеличивает количество каналов на микросхему DRAM, добавляет новые шаблоны обучения интерфейса и вводит встроенный ECC для поддержания эффективной надежности памяти.

«JESD239 GDDR7 знаменует собой существенный прогресс в разработке высокоскоростной памяти», — сказал Миан Куддус, председатель совета директоров JEDEC. «С переходом на сигнализацию PAM3 у индустрии памяти появился новый путь к повышению производительности устройств GDDR и стимулированию продолжающейся эволюции графики и различных высокопроизводительных приложений».

GDDR7 находится в разработке уже несколько лет, и члены JEDEC сделали первые открытия о технологии памяти около года назад, когда компания Cadence сообщила об использовании кодировки PAM3 как части своих инструментов проверки. С тех пор мы слышали от нескольких производителей памяти, что выпуск финальной версии памяти следует ожидать в 2024 году, причем объявление JEDEC, по сути, происходит точно по графику.

Как было показано ранее, самое большое техническое изменение в GDDR7 связано с переходом от двухбитного кодирования без возврата к нулю (NRZ) на шине памяти к трехбитному кодированию с амплитудной модуляцией импульсов (PAM3). Это изменение позволяет GDDR7 передавать 3 бита за два цикла, что на 50% больше данных, чем GDDR6, работающая на той же тактовой частоте. В результате GDDR7 может поддерживать более высокие общие скорости передачи данных, что является критически важным компонентом, позволяющим сделать каждое поколение GDDR более быстрым, чем его предшественник.

| Поколения ГДДР | |||||

| ГДДР7 | GDDR6X (Не JEDEC) |

ГДДР6 | |||

| Ч/Б на контакт | 32 Гбит/с (1-е поколение) 48 Гбит/с (максимальная спецификация) |

24 Гбит/с (доставка) | 24 Гбит/с (выборка) | ||

| Плотность чипа | 2 ГБ (16 ГБ) | 2 ГБ (16 ГБ) | 2 ГБ (16 ГБ) | ||

| Всего ч/б (256-битная шина) | 1024 ГБ/сек. | 768 ГБ/сек. | 768 ГБ/сек. | ||

| Напряжение оперативной памяти | 1,2 В | 1,35 В | 1,35 В | ||

| Скорость передачи данных | КДР | КДР | КДР | ||

| Сигнализация | ПАМ-3 | ПАМ-4 | НРЗ (двоичный) | ||

| Максимальная плотность | 64 ГБ | 32 ГБ | 32 ГБ | ||

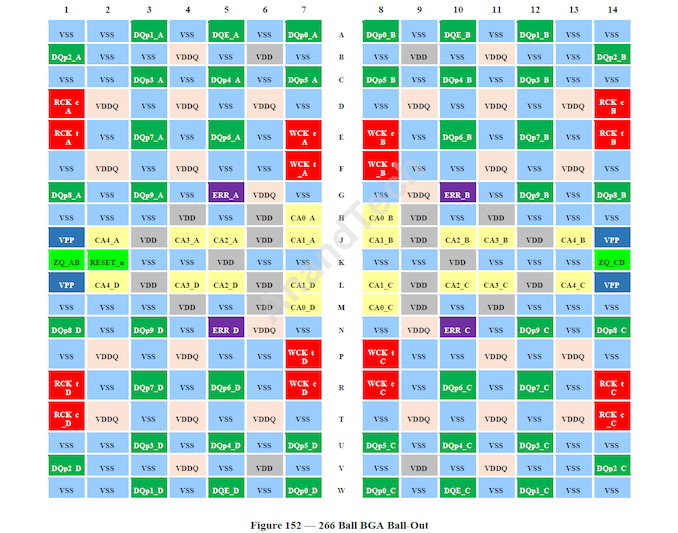

| Упаковка | 266 ФБГА | 180 ФБГА | 180 ФБГА | ||

Ожидается, что первое поколение GDDR7 будет работать со скоростью передачи данных около 32 Гбит/с на контакт, а производители памяти ранее говорили о скоростях до 36 Гбит/с на контакт как на легко достижимых. Однако сам стандарт GDDR7 оставляет место для еще более высоких скоростей передачи данных – до 48 Гбит/с/контакт – а JEDEC зашла так далеко, что рекламировала чипы памяти GDDR7, «достигающие скорости до 192 ГБ/с». [32b @ 48Gbps] на устройство» в их пресс-релизе. Примечательно, что это значительно большее увеличение пропускной способности, чем то, что обеспечивает сигнализация PAM3 сама по себе, а это означает, что в конструкции GDDR7 имеется несколько уровней улучшений.

Углубившись в спецификацию, JEDEC также снова разделил один 32-битный чип памяти GDDR на большее количество каналов. В то время как GDDR6 предлагал два 16-битных канала, GDDR7 расширяет их до четырех 8-битных каналов. Это различие несколько условно с точки зрения конечного пользователя – несмотря на это, это все равно 32-битный чип, работающий со скоростью 32 Гбит/с/контакт – но оно оказывает большое влияние на внутреннюю работу чипа. Тем более, что JEDEC сохранил 256-битную предварительную выборку на канал GDDR5 и GDDR6, что делает GDDR7 структурой предварительной выборки 32n.

Архитектура канала GDDR. Оригинальная схема эпохи GDDR6 предоставлена Micron

Конечным результатом всего этого является то, что, уменьшив вдвое ширину канала, но сохранив размер предварительной выборки тем же, JEDEC фактически удвоил объем данных, предварительно извлекаемых за цикл ячеек DRAM. Это довольно стандартный трюк для расширения пропускной способности памяти DRAM, и по сути это то же самое, что JEDEC сделал с GDDR6 в 2018 году. Но он служит напоминанием о том, что ячейки DRAM по-прежнему очень медленны (порядка сотен МГц) и не становятся быстрее. Таким образом, единственный способ обеспечить более быстрые шины памяти — это получать все большие объемы данных за один проход.

Изменение количества каналов на микросхему памяти также оказывает незначительное влияние на работу многоканального режима «раскладушки» для конфигураций памяти большей емкости. В то время как GDDR6 имеет доступ к одному каналу памяти каждого чипа в конфигурации «раскладушка», GDDR7 будет иметь доступ к двум каналам – то, что JEDEC называет двухканальным режимом. В частности, этот режим считывает каналы A и C с каждого чипа. По сути, это идентично тому, как режим раскладушки вел себя с GDDR6, и это означает, что, хотя конфигурации раскладушки по-прежнему поддерживаются в этом последнем поколении памяти, не используется никаких других уловок для увеличения емкости памяти, кроме постоянно растущей плотности микросхем памяти.

В связи с этим стандарт GDDR7 официально добавляет поддержку устройств DRAM 64 Гбит, что вдвое превышает максимальную емкость GDDR6/GDDR6X в 32 Гбит. Также продолжает поддерживаться емкость, не равная степени двойки, что позволяет использовать чипы 24 Гбит и 48 Гбит. Поддержка чипов памяти большего размера еще больше увеличивает максимальный объем памяти теоретической видеокарты высокого класса с 384-битной шиной памяти до 192 ГБ памяти – развитие, которое, несомненно, приветствовалось бы операторами центров обработки данных в эпоху больших языковые модели ИИ. Однако, несмотря на вышесказанное, мы по-прежнему регулярно видим чипы памяти 16 Гбит, используемые на современных картах памяти, хотя GDDR6 поддерживает чипы 32 Гбит. В сочетании с тем фактом, что Samsung и Micron уже сообщили, что их первое поколение чипов GDDR7 также будет иметь максимальную скорость 16 Гбит/24 Гбит соответственно, можно с уверенностью сказать, что чипы 64 Гбит в будущем довольно далеки (так что не продавайте ваши карты емкостью 48 ГБ еще не отключены).

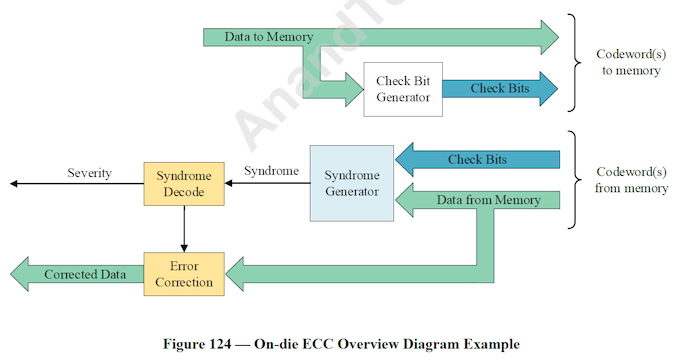

В своем последнем поколении технологий памяти JEDEC также включает несколько новых функций надежности памяти GDDR. В частности, встроенные возможности ECC, аналогичные тем, которые мы видели с появлением DDR5. И хотя нам не удалось получить официальный комментарий от JEDEC о том, почему они решили включить поддержку ECC именно сейчас, ее включение неудивительно, учитывая требования к надежности для DDR5. Короче говоря, по мере увеличения плотности чипов памяти становится все труднее создать «идеальный» кристалл без каких-либо дефектов; поэтому добавление встроенного ECC позволяет производителям памяти обеспечивать надежную работу своих чипов даже при возникновении неизбежных ошибок.

Этот рисунок воспроизведен с разрешения из документа JEDEC JESD239, рисунок 124.

Внутренняя спецификация GDDR7 требует минимум 16 бит данных четности на 256 бит пользовательских данных (6,25%), при этом JEDEC приводит пример реализации 9-битного кода с исправлением одиночных ошибок (SEC) плюс 7-битной циклической избыточности. проверка (CRC). В целом, встроенная ECC GDDR7 должна быть способна исправлять 100% 1-битных ошибок и обнаруживать 100% 2-битных ошибок, а в редких случаях 3-битных ошибок этот показатель снижается до 99,3%. Информация об ошибках памяти также предоставляется контроллеру памяти через встроенный в JEDEC протокол прозрачности ECC. И хотя технически GDDR7 отделен от самого ECC, он также включает еще одну функцию надежности памяти с четностью командного адреса с блокировкой команд (CAPARBLK), которая предназначена для улучшения целостности шины командного адреса.

В противном случае, хотя включение встроенного ECC вряд ли окажет большее влияние на потребительские видеокарты, чем его включение на память DDR5 и потребительские платформы, еще неизвестно, что это будет означать для рабочих станций и серверов. видеокарты. Тамошние поставщики уже несколько поколений используют программный ECC поверх незащищенной памяти; предположительно, это останется верным и для карт GDDR7, но регулярное использование программного ECC делает ситуацию намного более гибкой, чем в пространстве ЦП.

Этот рисунок воспроизведен с разрешения из документа JEDEC JESD239, рисунок 152.

Наконец, GDDR7 также представляет набор других функций, связанных с надежностью, в первую очередь связанных с поддержкой работы PAM3. Сюда входят базовые независимые шаблоны обучения LFSR (регистр сдвига с линейной обратной связью) с маскированием глаз и счетчиками ошибок. Шаблоны обучения LFSR используются для тестирования и настройки интерфейса (для обеспечения эффективности), маскирование глаз оценивает качество сигнала, а счетчики ошибок отслеживают количество ошибок во время обучения.

Помимо технических вопросов, объявление на этой неделе включает заявления о поддержке со стороны всех обычных игроков с обеих сторон острова, включая AMD и NVIDA, а также Micron/Samsung/SKhynix trifecta. Само собой разумеется, что все стороны заинтересованы в том, чтобы использовать или продавать GDDR7 соответственно, учитывая увеличение емкости памяти и пропускной способности, которое она принесет – и особенно в нашу эпоху, когда все, предназначенное для рынка искусственного интеллекта, продается как горячие пирожки.

В настоящее время не анонсируется никаких конкретных продуктов, но поскольку Samsung и Micron ранее объявили о своем намерении выпустить память GDDR7 в этом году, мы должны увидеть новую память (и новые графические процессоры для ее сопряжения) позднее в этом году.

Авторские права на стандарты и публикации JEDEC принадлежат Ассоциации твердотельных технологий JEDEC. Все права защищены.

www.anandtech.com