Архитектура Intel Meteor Lake для мобильных ПК скоро появится, и сказать, что Meteor Lake — это самый важный сдвиг в подходе Intel к проектированию и производству, значит не сказать ничего. Фактически, Intel назвала Meteor Lake крупнейшим архитектурным сдвигом за последние 40 лет, и он будет влиять на дизайн в течение следующего десятилетия.

Intel обозначила четыре ключевых принципа развития Meteor Lake. Во-первых, он спроектирован как самый энергоэффективный клиентский процессор в истории компании. Во-вторых, это будет первый потребительский процессор Intel, предлагающий специализированный механизм искусственного интеллекта в большом масштабе. В-третьих, Intel нацелена на скачок в производительности графики наряду с энергоэффективностью. Наконец, это будет дебют процесса Intel 4, по крайней мере частично.

Intel делает ставку на дезагрегацию с помощью Meteor Lake

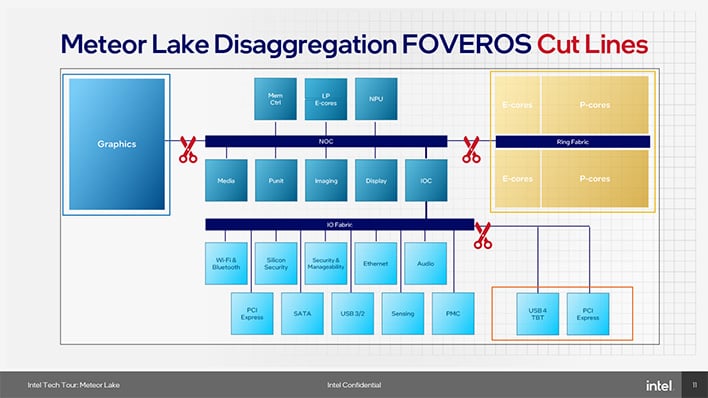

Meteor Lake — первый по-настоящему дезагрегированный потребительский чип компании, и его разработка была сложной задачей. Дезагрегация означает, что вместо использования одного монолитного кристалла для размещения ядер ЦП, встроенного графического процессора, функций ввода-вывода и других неядерных «вещей», различные механизмы вместо этого разбиваются на несколько чиплетов, которые Intel называет плитками.

Это привлекательный подход по многим причинам. Штампы могут быть изготовлены только такого размера, оставаясь при этом экономически и физически осуществимыми. Текущие процессы ограничены размерами сетки во время литографического травления, но нужно учитывать не только этот (более или менее) жесткий предел. Более крупный кристалл не только имеет больше «бесполезного» пространства по краям круглой 300-миллиметровой пластины, но также с большей вероятностью будет иметь изнурительные дефекты, что оказывает прямое негативное влияние на выход продукции. Чипы меньшего размера позволяют производителям извлекать больше из каждой пластины, максимизируя потенциальную ценность каждой.

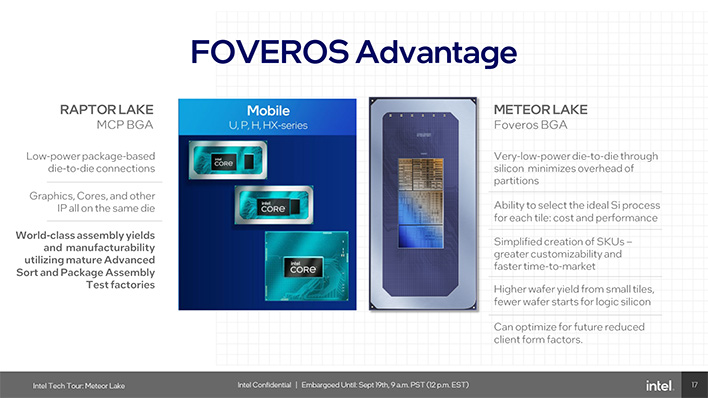

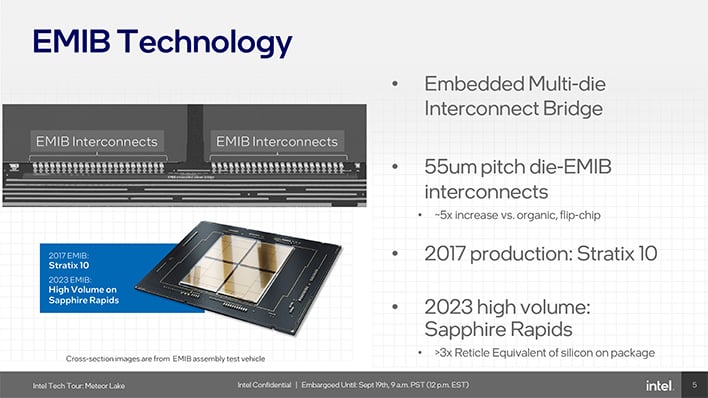

Разбиение проекта на более мелкие чипсеты, конечно, имеет свои недостатки. Упаковать все это вместе становится намного сложнее, независимо от того, как вы это разбиваете. Если мы на мгновение отбросим 3D V-Cache, AMD размещает чиплеты вокруг друг друга на одной печатной плате для своих процессоров, тогда как Intel предпочитает размещать кремний напрямую, используя технологии Foveros и Embedded Multi-die Interconnect Bridge (EMIB). Foveros и EMIB похожи, но отличаются передовыми технологиями упаковки, которые Intel использует в некоторых продуктах уже несколько лет.

EMIB впервые дебютировал в 2017 году в Stratix 10. Это был чип с программируемой решетчатой матрицей (FPGA), но технология переросла в крупносерийное производство и сегодня используется Sapphire Rapids. EMIB использует межсоединения с шагом 55 мкм для установки кристалла на встроенный кремниевый мост.

Foveros позволяет выполнять укладку «активный-активный» в режиме «3D» с большей сложностью. Foveros был представлен в Lakefield в 2020 году, где он позволил Intel разместить вычислительный кристалл с PoP DRAM поверх базового кристалла, который затем монтируется на подложку корпуса.

Встречайте плитки Метеоритного озера

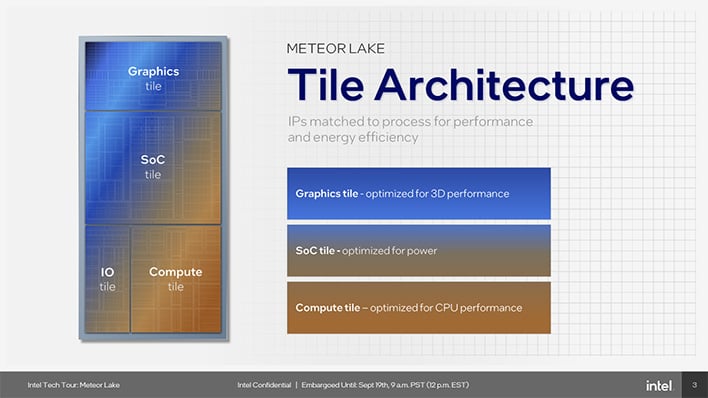

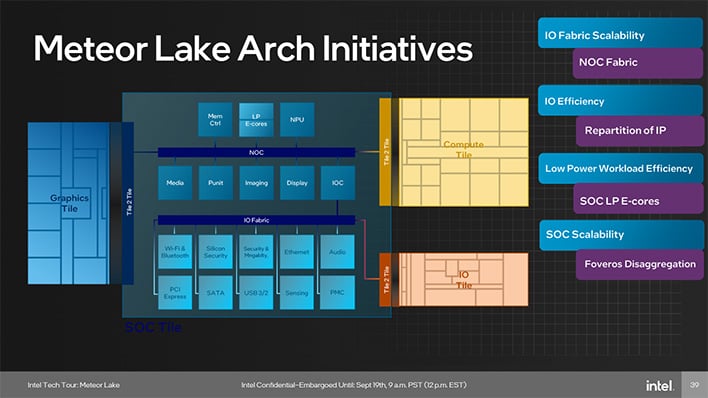

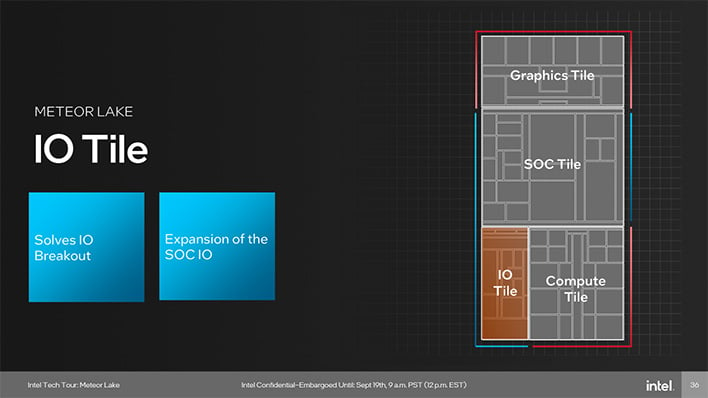

В дизайне Meteor Lake используются четыре отдельные плитки, расположенные поверх базовой плитки, собранной с использованием технологии упаковки Foveros 3D. Это плитка вычислений, плитка графического процессора, плитка SOC и плитка ввода-вывода соответственно, что дает некоторое представление об основной функции каждого из них. Однако здесь, безусловно, есть некоторые нюансы, поэтому давайте быстро рассмотрим высокоуровневые атрибуты каждого из них, прежде чем копать глубже.

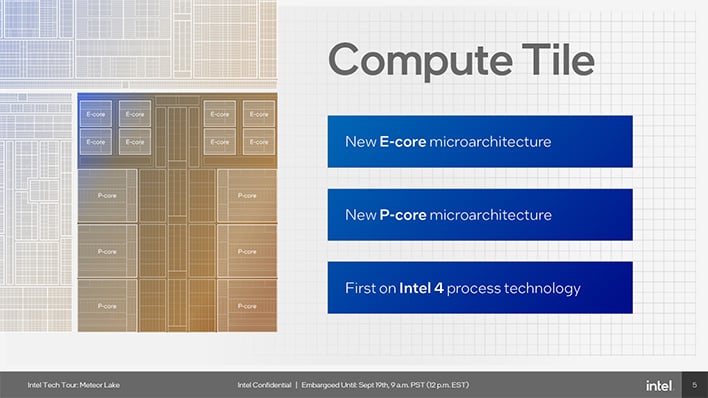

На плитке «Вычисления» находится большинство ядер процессора. Большинство, спросите вы? Мы доберемся до этого. Плитка Compute представляет собой смесь P-ядер и E-ядер, к которым мы привыкли из Alder Lake и Raptor Lake, с некоторыми микроархитектурными улучшениями. Плитка «Вычисления» построена с использованием узла процесса Intel 4 и фактически является единственной плиткой в системе, созданной непосредственно Intel.

Плитка графического процессора следующая. Как и ожидалось, он содержит архитектуру Intel Arc Graphics, в частности Xe-LPG. Это разработано TSMC на основе процесса N5 и предназначено для обеспечения примерно двукратного повышения производительности на ватт по сравнению с графикой Xe 12-го поколения. Однако плитка «Графика» не содержит Media Engine. Он был выделен и размещен на плитке SOC вместе с интерфейсами дисплея.

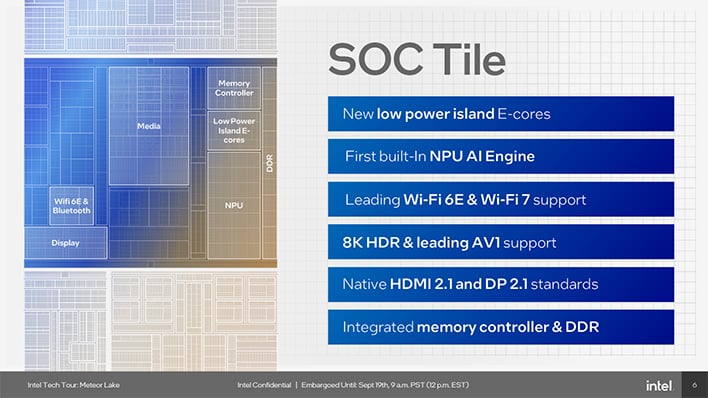

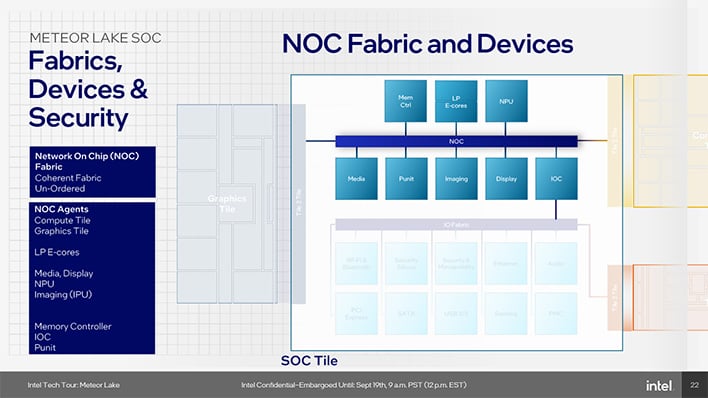

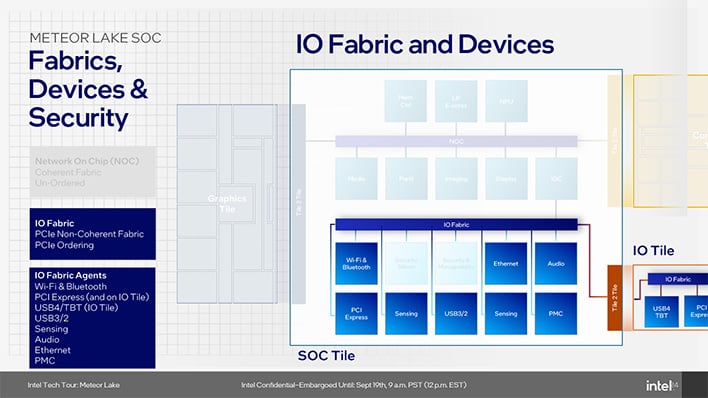

Плитка SOC — это хранилище широкого спектра функций в двух масштабируемых фабриках. Северная сторона оснащена фабрикой Network on Chip (NOC), соединяющей высокопроизводительные устройства, а южная сторона имеет эффективную фабрику ввода-вывода на основе PCIe с мостом IOC, соединяющим их. Помимо возможностей подключения и механизмов мультимедиа/дисплея, он также содержит механизм искусственного интеллекта NPU, контроллер памяти и два собственных специальных электронных ядра. Плитка ввода-вывода действует как расширение структуры ввода-вывода плитки SOC, и обе они создаются с использованием процесса N6 TSMC.

Подробности о плитках SOC и IO

Углубляясь в архитектуру, давайте начнем с плитки SOC. Он находится в центре всего и напрямую связан с плитками «Вычисления», «Графика» и «IO». По сути, именно в этих связях были сделаны «сокращения», чтобы вырваться из традиционного подхода, основанного на монолитном штампе. Если мы на мгновение вернемся назад, архитектура SOC обманчиво сложна и влияет на процессы, инициированные фабрикой, и на возможность запуска новых узлов. Такое разбиение чипа освобождает архитекторам возможность работать с производственными процессами, подходящими для IP. Дезагрегирование гарантирует, что Compute Tile будущих продуктов, например, сможет быстро перейти на Intel 3 и выше, в то время как другие части SOC, которые, возможно, не получат особой выгоды от более продвинутых узлов процессов, смогут развиваться более медленными темпами.

Архитектурные изменения и философия дизайна Meteor Lake были вызваны несколькими инициативами. Первым было внедрение структуры NOC для удовлетворения требований высокопроизводительных устройств, в то же время позволив фабрике ввода-вывода обеспечить эффективный доступ при более низком энергопотреблении. Чтобы повысить эффективность ввода-вывода, Intel переместила графику в отдельную плитку, но сохранила блоки мультимедиа и дисплея в плитке SOC. Наконец, система управления электропитанием должна была быть масштабируемой, с возможностью контроля над каждым элементом и даже подсистемами внутри каждого элемента. Например, это позволяет настроить PMC для вычислительной плитки на количество доступных P- и E-ядер, в то время как центральный PMC на плитке SOC не зависит от конфигурации вычислительной плитки.

«Северная» структура NOC — это неупорядоченный интерфейс с когерентным кэшем, охватывающий весь тайл SOC, от вычислительного тайла до графического тайла. Внутри плитки SOC он связывает высокопроизводительные устройства, такие как контроллер памяти, электронные ядра LP, блок нейронной обработки (NPU), а также механизмы мультимедиа, обработки изображений и отображения. Он также имеет локальный блок управления питанием (P-Unit) для регионального управления, что приводит к повышению эффективности.

Включение LP E-ядер в SOC — интересное решение со значительными последствиями, особенно для Thread Director. Конструкция позволяет этой паре ядер оставаться активными, даже когда вычислительный модуль находится в режиме пониженного энергопотребления или полностью отключен. В результате это создает большой потенциал для значительного повышения эффективности Meteor Lake в обычных условиях использования.

«Южная» фабрика ввода-вывода упорядочена, но некогерентна и основана на PCIe. Он является домом для Wi-Fi и Bluetooth, соединений PCI Express, Sensing, USB 3/2, Ethernet, контроллера управления питанием (PMC) и контроллеров безопасности. Intel выделила Silicon Security Engine из своего традиционного Converged Security and Manageability Engine (CSME).

Панель ввода-вывода обеспечивает дополнительные возможности подключения PCI Express и USB4/Thunderbolt с использованием структуры ввода-вывода. Расположение плитки ввода-вывода рядом с вычислительной плиткой является намеренным, поскольку такая конфигурация эффективно увеличивает площадь поверхности SOC, делая внешние соединения менее перегруженными.

Но еще многое предстоит охватить…